算力核心赛道:ASIC芯片全解析

热门主题产业链

当前全球AI算力需求强劲,随着算力重心由训练端加速转向推理端,ASIC作为推理主要形式景气度持续上升。

此外,科技巨头和云服务商加速推进ASIC业务,近期博通和Marvell业绩指引高于预期,而在AI网络方面,ScaleUp/Out/Across也带来ASIC强劲增长。

Marvell预计,到2028年全球AI ASIC市场规模将达到554亿美元。

在ASIC产业趋势确定背景下,其高度定制化和能效优势趋势逐渐清晰,有望重塑全球算力市场格局,国产ASIC产业链各环节在此背景下也有望迎来新一轮机遇。

在之前的文章中,我们梳理了国产算力数据中心核心赛道、液冷服务器零部件全梳理、光模块全解析

本文重点解析算力高增长赛道:ASIC芯片。

01ASIC行业概览

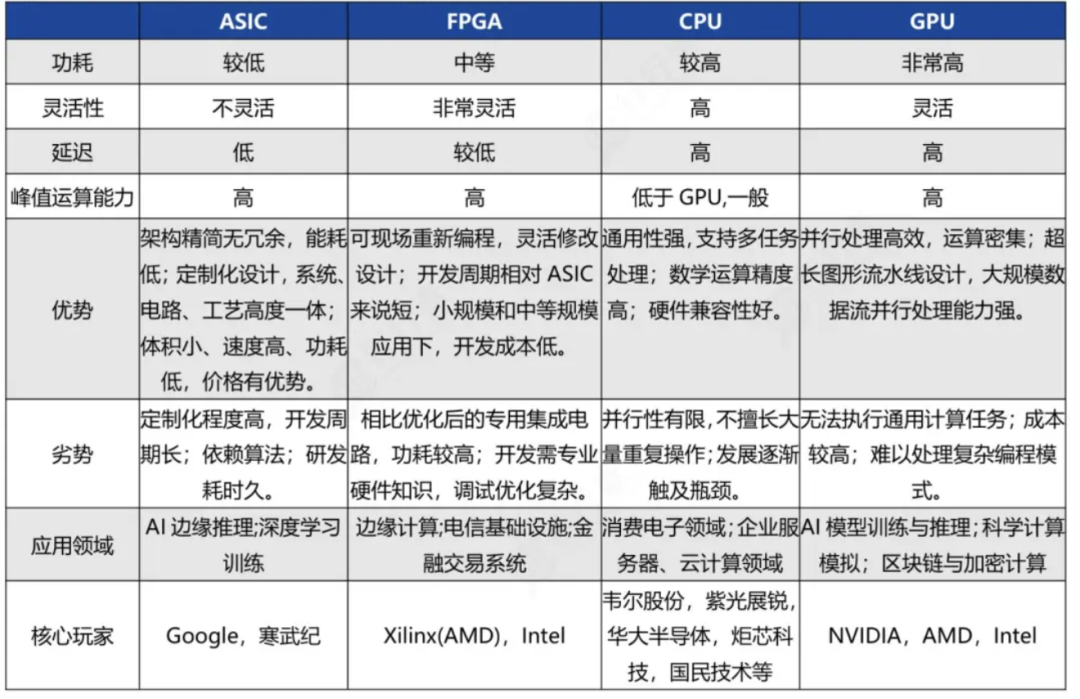

算力芯片主要有CPU、GPU、FPGA和ASIC四种形式。

这几种芯片架构在功耗、价格和性能上各有侧重,适用于不同场景的需求。

算力芯片对比:

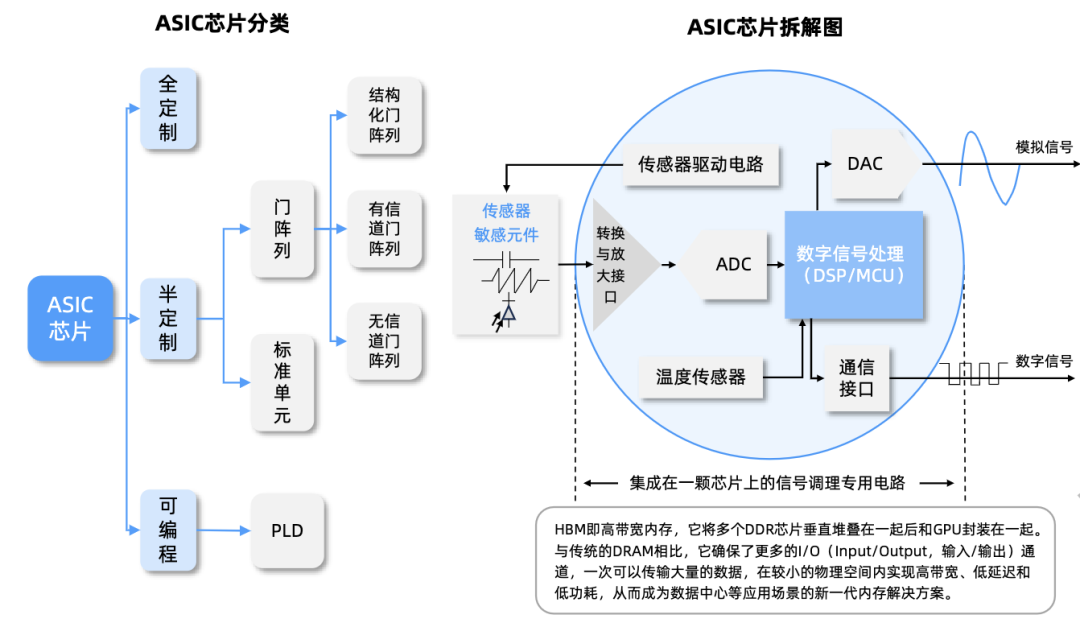

ASIC芯片即专用集成电路,是针对特定应用需求而设计和定制的芯片。

与GPU和FPGA比较:GPU通用性强但功耗高,FPGA灵活性好但成本较高。ASIC具备高专用性和高性价比的特征,在性能、功耗和体积方面表现更优,主要应用于云端和终端推理场景。

ASIC的限制和优势:ASIC芯片设计的前期投入较高,一旦设计完成难以更改,这限制了其对于新算法、新任务的适用能力。近几年随着云厂商对AI算力的需求扩张,AI推理等特定场景需求加速,ASIC方案在性价比上的优势日益凸显。

当前AI由投资驱动转向应用拉动,推理需求成为AI云和端侧的主要成长动能,JPM预计2026年开始占比有望超过60%。

ASIC芯片拆解图:

资料来源:行行查

资料来源:行行查

02

ASIC产业链

ASIC产业链上游主要包括底层算法设计企业、IP核授权企业、EDA工具供应商等;中游是ASIC芯片生产制造环节,包括ASIC芯片制造商、流片和封测等厂商;下游应用于通信、消费电子、汽车、工控和AI等大领域。

上游

底层算法设计

ASIC的底层算法设计是芯片性能的核心驱动力,直接影响芯片在特定应用场景中的能效比、计算密度和成本竞争力,其底层算法设计遵循“算法-架构-硬件”协同优化原则。包括高通、ARM、谷歌(TPU架构)、英特尔(Xeon架构)等主导算法架构;寒武纪(思元系列)、阿里平头哥(含光系列)等国内企业加速突破。

IP核授权

IP核是经过验证的、可复用的集成电路设计模块,其核心价值在于通过标准化设计降低芯片开发成本,并且缩短周期并提升可靠性。

ASIC芯片设计高度依赖IP核,在高性能计算、AI加速和通信基带等复杂场景,IP核复用率可达70%以上。从全球竞争格局来看,ARM(处理器IP)、Synopsys(接口IP)、Cadence(存储IP)等占据全球市场绝大部分份额,国内企业如芯原等针对处理器IP有较深技术积累,其他部分如先进封装Chiplet等正在积极布局。

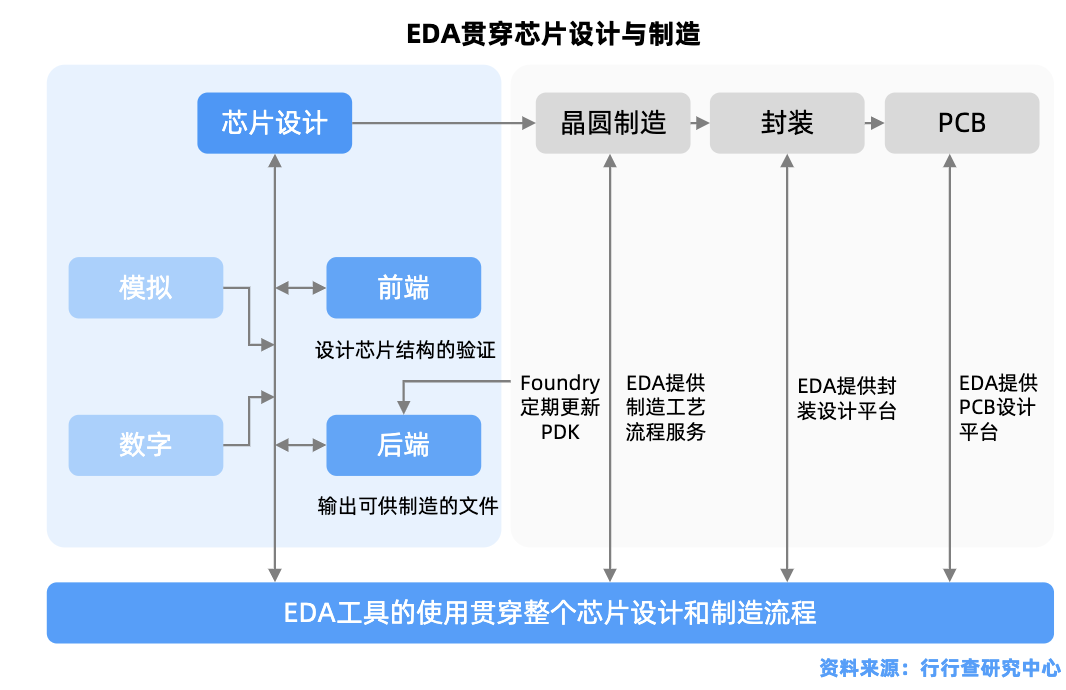

EDA工具

在设计ASIC芯片的过程中,EDA决定设计效率与流片成功率。

利用EDA工具,设计师可以对ASIC芯片进行全面的仿真和验证,从而确保设计的正确性和可行性。

Synopsys、Cadence、西门子EDA占据全球80%以上市场份额,覆盖设计全流程(前端仿真、后端布局布线、签核验证)。 国产替代主要厂商中,华大九天(模拟/面板/存储/射频全流程)、概伦电子(存储器设计平台)、广立微(良率分析与测试设备)等企业逐步实现点工具突破。

中游:ASIC芯片设计/制造

前端:云厂商设计团队提出需求,实际芯片架构设计、逻辑设计等仍需依赖专业芯片设计团队(可能为云厂商自有或外包);当前CSP也正在组建大型芯片设计工程师团队。

定制芯片主要包含四部分IP,计算、存储、网络I/O及封装。服务提供商不涉及计算部分架构设计,只提供相应设计流程及性能优化。

后端:由于云厂商在芯片设计能力上具有局限性,大多没有能力完成独立的SoC设计,因此往往会寻求与半导体公司进行合作。

在ASIC产业链的供给侧,目前全球两家最大的ASIC半导体公司是博通和Marvell,目前两家公司占据了超过60%的份额。博通以55%-60%份额位居第一,Marvell以13%-15%的份额位居第二。博通、Marvell能提供存储、网络I/O、封装的完整IP解决方案。

大型云服务厂商多与以上两者合作,比如谷歌的TPU就是与博通合作开发的,Marvell联手亚马逊。

流片:流片Tape-out是指设计完整的芯片电路后,将其转换为物理芯片的过程,是集成电路设计的最后环节,也是送交制造的关键步骤。这一环节也是ASIC芯片制造中最重要、最耗钱的环节之一。在流片环节主要参与厂商包括台积电、中芯、华虹等大厂。

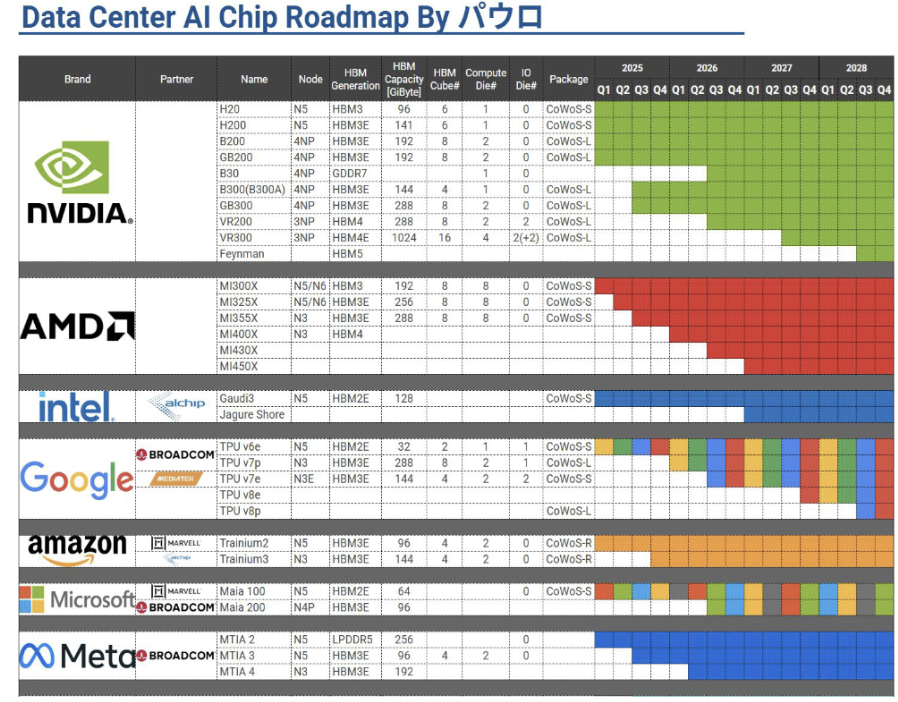

近年来,云厂商自研芯片势头强劲,ASIC正成为全球云厂商及AI模型企业的核心布局方向。

谷歌TPU最早发力ASIC市场,TPUv5成本较英伟达方案降低40%,自用率超70%;AWS紧随其后自研芯片AWSTrainium2;微软Maia加速扩张;MetaASIC实现性能跃迁。

国内百度、阿里和腾讯等互联网大厂自研AI芯片大多采用ASIC架构,主要应用于自身业务场景,典型的ASIC芯片例如:阿里平头哥推出含光800AI芯片;百度昆仑系列AI芯片。HW、寒武纪、燧原科技、黑芝麻和地平线等厂商也基于ASIC架构设计芯片,在深度学习模型的训练和推理方面具有高性能和高效率。ASIC产业链各环节相关布局厂商还包括如翱捷科技、全志科技、澜起科技、瑞芯微、灿芯股份、国科微、淳中科技、山石网科等。

各家CSP厂商均在布局ASIC方案:

数据来源:智猩猩芯算,パウロ

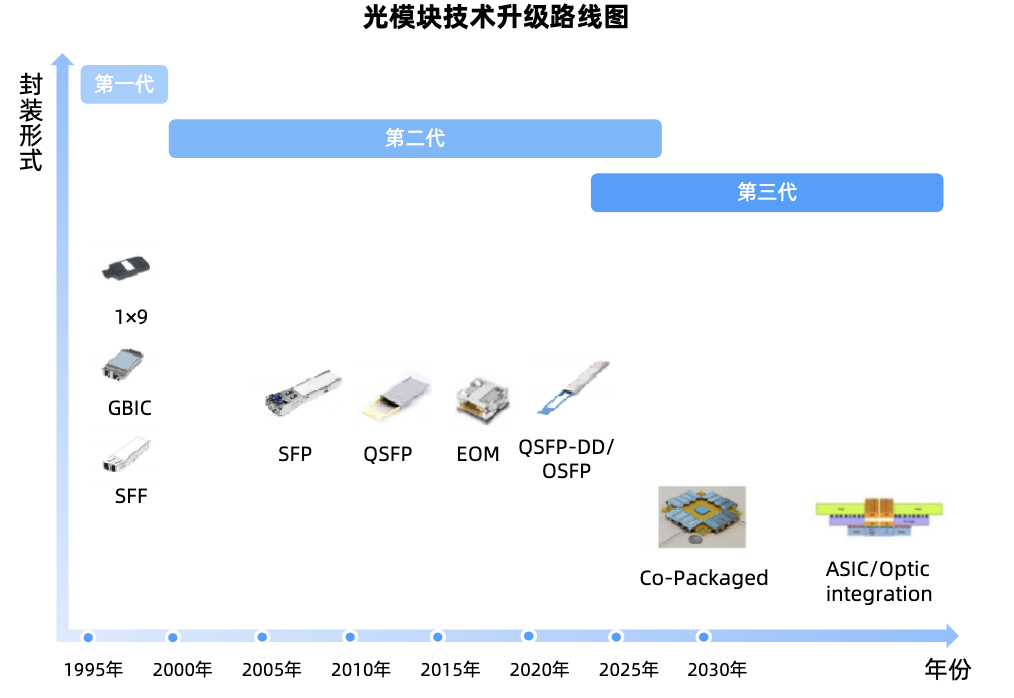

由于ASIC方案对工艺、封装、测试等环节提出更高要求,也带动产业链中的光模块、AEC、液冷、PCB、先进封装等各环节需求增长。

光模块:超大规模ASIC部署使得架构层数增加,带动光模块用量和相关新技术水涨船高。交换芯片升级推动光模块端口速率提升,配套800G光模块以及更高速率的1.6T以太网光模块持续推进,相关光模块和光芯片厂商加速布局。例如,网络架构变动最大的Meta链相关厂商旭创、新易盛、太辰光、源杰、仕佳光子;1.6T光模块26年上修相关厂商旭创、新易盛、天孚、汇绿生态等;国内厂商有望突破北美云厂商:联特、华工、光迅、剑桥;设备商/新云厂商需求的供应链剑桥、腾景、汇率生态等。

CPO:博通ASIC方案已积极储备CPO等技术,新一代CPO版本将集成光学引擎与交换硅片),进一步降低功耗、延迟与链路波动,提升长期可靠性。CPO技术可以缩短交换芯片和光引擎之间的距离,国内众多厂商在这一领域布局,天孚通信、罗博特科、剑桥、太辰光以及上游光芯片和MPO相关厂商博创、太辰光、仕佳光子、光库科技、源杰科技等。

资料来源:行行查

资料来源:行行查

高速铜缆连接:ASIC芯片数量的增加以及光、铜、PCB等数通设备配比的提高,推动铜连接市场放量。根据Semianalysis, AWS方案中GPU与AEC的用量配比为1:2,ASIC放量有望显著带动AEC需求。国内主要参与厂商包括兆龙互联、博创科技、沃尔核材、瑞可达、神宇股份、立讯精密、鼎通科技、长芯博创等;高速背板连接器主要参与厂商包括华丰科技、意华股份、庆虹电子、中航光电、陕西华达、神宇股份、鸿腾精密等。

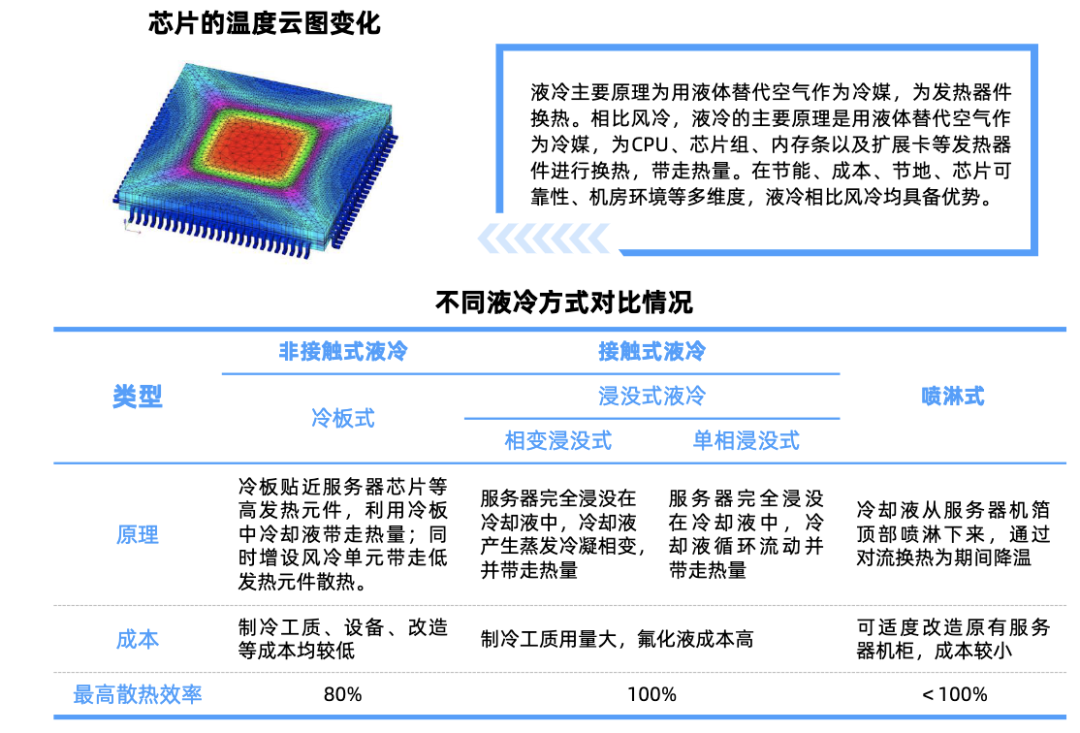

液冷:随着谷歌、微软、亚马逊、Meta自研ASIC芯片的不断迭代,算力性能增长相应带来单卡TDP(热设计功耗)快速提升,升级机架方案提升散热需求。国内液冷环节厂商众多,例如,英维克、申菱环境、高澜股份、银轮股份、科创新源等都全面进行布局。

PCB:ASIC芯片在算力密度上通常低于GPU,为弥补这一差距,需通过更高层数的PCB走线实现信号完整性和高速传输。从需求端来看,算力升级对PCB制程升级趋势明确。国产化进程全面提速,头部厂商胜宏、沪电、生益科技、景旺电子、深南电路、广合科技、南亚新材等在产业链各环节加速布局。

交换机:算力产业链上游实现网络互联的关键设备,通过电/光信号转发实现算力设施多设备间高效通信。中国交换机市场前五厂商份额约为89.7%,华为、新华三(紫光旗下)、锐捷网络、中兴通讯、思科形成高度集中格局。博通于6月初发布自家最新的Tomahawk6 102.4T数据中心交换芯片,在前代芯片基础上再次完成容量翻倍。国内盛科通信在商用以太网交换芯片国内排名第一,全球第四,800G芯片小批量交付,51.2Tbps国产芯片打破垄断,市场份额突破8%。

整体来看,当前全球算力持续爆发,AI推理需求强劲,叠加科技巨头和云厂商持续推进ASIC业务,ASIC及AI网络相关环节的发展有望呈现出新一轮高增长态势。

*免责声明:本文内容仅作为行业分析参考,不构成任何投资建议!

--------------

来源:乐晴智库精选

展开阅读全文

文章观点仅代表作者观点,或基于大数据智能生产,不构成投资建议。投资者依据此做出的投资决策需自担风险,与通联数据无关。