全环绕栅极(GAA)芯片架构技术商业进程解析!

大V说

线索主要标的

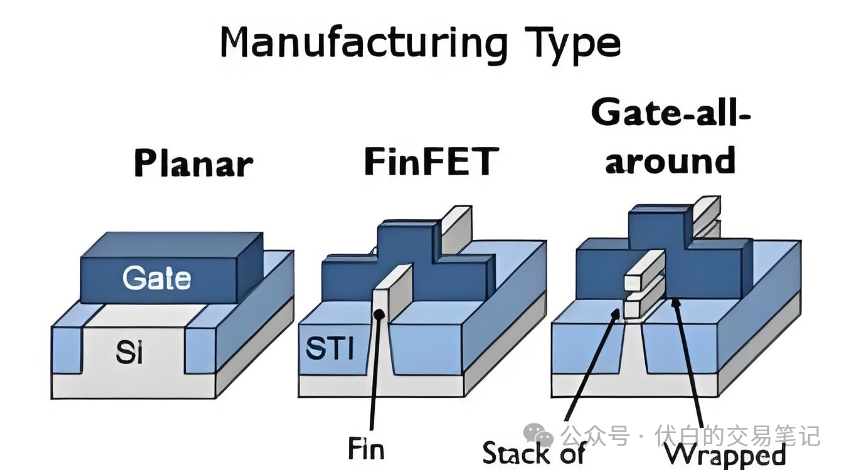

一. 芯片结构演变

晶体管是半导体的基础组成元件,一个芯片由小到几十、大到超百亿个晶体管构成。

晶体管具有调节和放大电流与开关的作用,其中最重要的部分就是栅极。

通常所说的芯片制程是栅极的长度,当芯片制程来到22nm以下时,栅极长度过短,造成栅极对器件开关的控制性能下降,会出现漏电现象。

因此在22nm制程以下,器件结构就由传统的平面2D结构转为3D的FinFET结构。

二. FinFET概览

FinFET就是将源极与栅极做薄做高,栅极与器件的接触面从原先的1面变为3面,有效减少了漏电流的发生,提高了晶体管的开关速度。

目前FinFET工艺已相当成熟,但随着器件结构进一步微缩,FinFET的静电问题制约了性能提升,出现计生电容、电阻问题。

三. GAA概览

GAA(Gate All Around),即全环绕栅极架构技术,相比FinFET结构,栅极的控制面由3面变为4面控制,从而实现对电流的更精确控制。

与传统的FinFET技术相比,GAA技术可以提供更高的性能和能效比、更低的功耗以及更小的芯片尺寸。

四. GAA工艺难点

相比Finfet,GAA因为要反复开槽、器件间距需要精确控制,因而工艺难度于步骤都大幅增加,对计量检测提出更高的要求。

材料、工艺方面,GAA的难点主要体现在:

(1)Epi Nanosheet:在硅基底上外延生产Si/SiGe叠层,需要精准控制外延沉积的厚度是工艺难点。

(2)recessing SiGe:开槽SiGe,刻蚀完SiGe后,在表面沉积一层介质绝缘层。

(3)recessing Si Depositing source&drain:关键步骤,在侧面刻蚀挖孔并沉积,经过清洗步骤后,完成掺杂硅的沉积。

(4)removing SiGe channels:要形成GAA的结构,必须要将SiGe材料去除,并且不对器件的源、漏产生影响。

(5)Tuning Gate:在源、漏电极表面沉积电极金属,精确计算沉积金属的厚度,工艺难度很大。

五. GAA商业进程

GAA主要用于3nm以下制程,目前在GAA工艺上布局的主要是台积电、三星、英特尔三家。

(1)三星:三星是最早宣布要量产GAA的厂商。三星在2022年宣布要在3nm节点引入GAA结构,目标在2025年量产2nm的GAA器件。

(2)台积电:台积电采取较为稳健的技术路线,3nm继续使用FinFET,未来将在2nm制程全面引入GAA工艺。

(3)英特尔:Intel将在2024-2025年全面引入RibbonFET(GAAFET),配合自研的背面供电,目标实现对台积电的弯道超车。

六. 国内相关厂商

GAA工艺核心在于多次刻蚀沉积:核心步骤通过原子层沉积(ALD)技术完成。

(1)刻蚀、沉积设备:北方华创、拓荆科技、中微公司、微导纳米。

(3)洁净室:柏诚股份。

来源:伏白的交易笔记

展开阅读全文

文章观点仅代表作者观点,或基于大数据智能生产,不构成投资建议。投资者依据此做出的投资决策需自担风险,与通联数据无关。